# SA400 minifloppy™Diskette Storage Drive with a Western Digital FD 1771 Controller and Motorola 6800 MPU

۵,

# System Implementation

SA4OO minifloppy<sup>™</sup> Diskette Storage Drive with a Western Digital FD 1771 Controller and Motorola 68OO MPU

© Copyright 1977 Shugart Associates

# Table of Contents

| 1.0 | Introducti<br>1.1 | on<br>General .                                                   |                     |                 |     |       | •    |             |   |   |   |   | • |   |             | • | •      |   |        |        |   | • | 1                      |

|-----|-------------------|-------------------------------------------------------------------|---------------------|-----------------|-----|-------|------|-------------|---|---|---|---|---|---|-------------|---|--------|---|--------|--------|---|---|------------------------|

| 2.0 | 2.1<br>2.2        | skette Drive<br>General .<br>Drive Perfo<br>Drive Inter           | <br>prmanc          | <br>се          | •   |       |      | <br>        | • | • | • | • | • | • |             | • |        | • | •      | •      |   | • | 3<br>3<br>3<br>3       |

| 3.0 | 3.1               | puter Syste<br>General .<br>Motorola 6                            |                     |                 | •   |       |      |             |   |   |   |   |   |   |             |   |        |   |        |        |   |   | 5<br>5<br>5            |

| 4.0 | 4.1<br>4.2<br>4.3 | igital FD17<br>General .<br>FD1771 Ir<br>Controller<br>Data Separ | <br>Iterfac<br>Comm | <br>e .<br>nand | Ini | itiat | tior | <br><br>1 . | • | • | • | • |   |   | •<br>•<br>• | • | •<br>• |   | •<br>• | •<br>• | • |   | 9<br>9<br>9<br>9<br>10 |

| 5.0 |                   | and Softwa<br>General                                             | are Co              |                 |     |       |      |             |   |   |   |   |   |   |             |   |        |   |        |        |   |   | 13<br>13               |

# List of Illustrations

Mill I a little to the little of the second second a

| 1. | FM Recommended Format | 1 |

|----|-----------------------|---|

| 2. | System Block Diagram  | 5 |

|    | System Schematic      |   |

| 4. | Sample Software       | 7 |

| 5. | Sample Software       | 1 |

## FORWARD

This Applications Bulletin is published as a "method" for using the SA400 Minifloppy Diskette Storage Drive. Shugart Associates does not assume responsibility for the use or implementation of this system nor any infringements of patents or other rights of third parties which may result from its use.

It is the intention of Shugart to publish further Applications Bulletins concerning various Microprocessors and single chip disk controllers/formatters.

#### **1.0 INTRODUCTION**

#### 1.1 General

This Application Bulletin briefly describes the parameters necessary to interface the SA400 Minifloppy<sup>TM</sup> Diskette Storage Drive with a Western Digital FD1771 Controller/Formatter, using a Motorola 6800 Microprocessor Unit (MPU) as the host computer system.

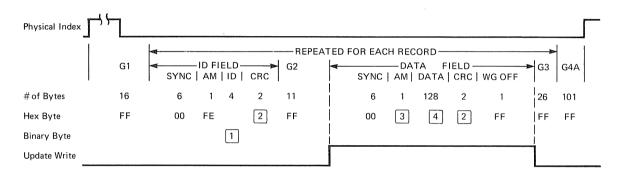

The discussion is based on a 16 sector, 128 byte per sector format as shown in Figure 1. References to a byte will be to an 8 bit byte with bit cell 0 being the most significant bit.

1 Track Addr, Zeroes, Sector Addr, Zeroes

2 Generated by CRC Generator

3 FB for Data Field or F8 for Deleted Data Field

4 User Data

FIGURE 1. FM RECOMMENDED FORMAT - 128 Byte & 16 Records/Track (IBM Type)

### 2.0 SA400 MINIDISKETTE DRIVE

#### 2.1 General

The SA400 Minifloppy Diskette Drive is a magnetic media storage device organized as 35 independent tracks with track zero being the outer most track with respect to the center of the disk.

Each track has a capacity of 3125 bytes (unformatted), hence a total disk capacity of 109.4 K bytes.

When formatted using the format shown in Figure 1, each track will have a user data capacity of 2048 bytes for a total user capacity of 71.68 K bytes. Up to three SA400 drives can be daisy chained on a single bus to provide 215 K bytes of user data storage.

#### 2.2 Drive Performance

The basic serial data rate of drive is 125 K bits per second which translates to 15.6 K bytes per second or 1 byte transferred every 64 microseconds.

The SA400 contains a D.C. spindle drive motor with an interface on/off control. To insure maximum motor life, the motor should be turned off when no further disk commands are anticipated. When turning the motor on, the host computer system should allow for a spindle motor up to speed and settle time of 1 second.

Each track of the disk drive can be accessed in 40 milliseconds with an additional 10 milliseconds of track settle time. The track settle time is not cumulative, that is, when performing multiple steps it is added only to the last track accessed.

The head load can be activated either from the spindle motor "ON" control signal or by selecting the drive. With either method a delay of 75 milliseconds is necessary after head load.

#### 2.3 Drive Interface

The SA400 is interfaced by 12 TTL compatable signals. The following interface signals are accompanied by a brief description. For further information refer to the SA400 OEM Manual.

Read Data (Output) – This signal is the digitized serial data, read from the diskette.

Write Data (Input) – This signal is the digitized serial data to be written on the diskette.

Write Gate (Input) – When activated, this signal causes 'write data' to be written on the diskette.

Write Protect (Output) – Indicates a write protected diskette has been inserted in the drive.

Step (Input) – For each step pulse, the R/W head moves one track.

Direction Select (Input) – Selects the direction of the R/W head will move when a pulse occurs on the 'step' line.

Track 00 (Output) – This signal indicates when the R/W head is positioned over track 0.

Drive Select (Input) -- 3 Lines to assign logical drive address.

Index/Sector (Output) – Pulse indicating that the physical index/sector hole of the diskette has passed over the index sensor.

Motor On (Input) – This signal controls spindle motor on/off.

#### 3.0 HOST COMPUTER SYSTEM

#### 3.1 General

The Motorola 6800 Microprocessor (MPU) is a monolithic 8 bit microprocessor forming the host system for this application.

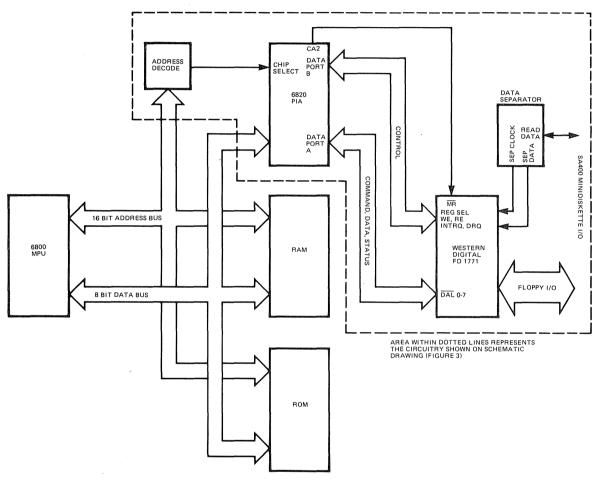

Peripheral I/O control is treated as a memory address (Memory Mapped I/O). A typical memory mapped I/O diagram is shown in Figure 2.

**FIGURE 2**

#### 3.2 Motorola 6820 Peripheral Interface Adapter

The FD1771 is interfaced to the 6800 through the 6820 peripheral interface adapter (PIA) which is treated as a memory address (Figure 2). All commands, data, status, and control are handled by the PIA.

The PIA provides a universal means of adapting peripheral devices to the 6800 PMU. The PIA interfaces the MPU through (2) 8 bit bidirectional data buses (ports) and 4 control lines.

During system initialization, the PIA is programmed to select the direction of each bit of the two ports as well as the functions of the 4 control lines (see Figure 4).

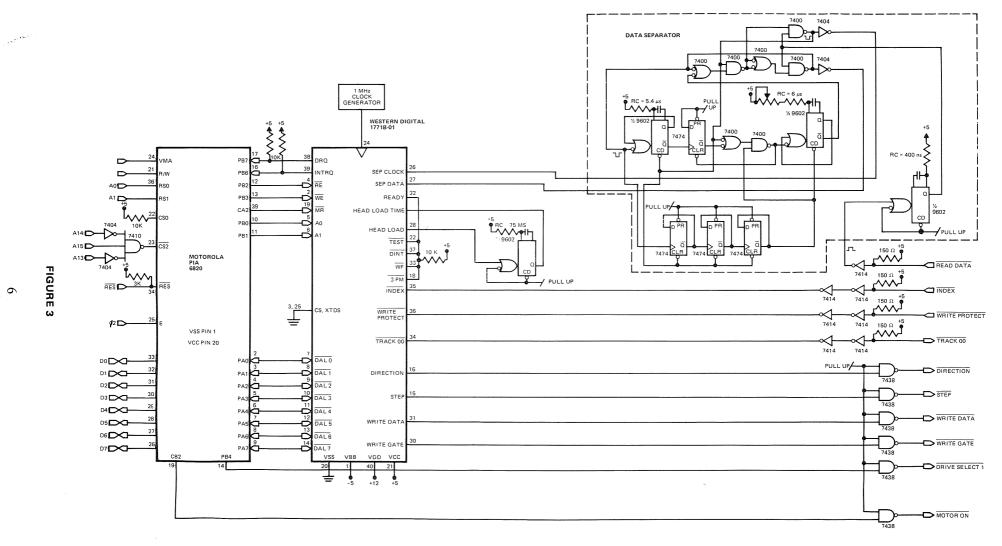

In this application, data port 'A' will interface to the FD1771 data lines. Port 'B' will interface to the various control lines of the FD1771 and the disk drive select lines. Two of the control lines are used for master reset of the FD1771 and control of the disk drive motor on/off (see Figure 3).

The I/O address of the PIA is selected so as not to overlap a memory address.

| <b>ÞAG</b> I | E I        | 001                         | W      | D/4    | 00 INIT d                                               | & INTERP I   | ROUTINES     |                          |                     |  |  |

|--------------|------------|-----------------------------|--------|--------|---------------------------------------------------------|--------------|--------------|--------------------------|---------------------|--|--|

|              | _          |                             |        | _,.    |                                                         |              |              |                          |                     |  |  |

| 0000         | 1          |                             |        |        |                                                         | TTL          |              | IIT & INTERP ROUTINES    |                     |  |  |

| 0000         |            |                             |        |        |                                                         | OPT          | REL,CREF     |                          |                     |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | NED TO PERFORM SEEKS,    |                     |  |  |

| 0000         |            |                             |        |        | <ul> <li>READS,WRITES, AND FORMATS USING THE</li> </ul> |              |              |                          |                     |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | 1 FLOPPY CONTROLLER CH   | IP                  |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | 0 AND A MOTOROLA 6800    |                     |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | COMMANDS ARE ENTERED     |                     |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | CONSOLE IN THE FORM OF A |                     |  |  |

| 0000         |            |                             |        |        |                                                         |              |              | CHARACTERS (HEX NOTAT    |                     |  |  |

| 0001         |            |                             |        |        |                                                         | T OK 2 FAI   | NAMETER      | CHARACTERS (HEA NOTAT    | ION)                |  |  |

| 0001         |            |                             | 8401   | А      | CRA                                                     | EQU          | \$8401       |                          |                     |  |  |

| 0001         |            |                             | 8403   |        | CRB                                                     | EQU          | \$8403       |                          |                     |  |  |

| 0001         |            |                             | 8400   |        | PORTA                                                   | -            | \$8400       |                          |                     |  |  |

| 0001         |            |                             | 8402   |        | PORTB                                                   |              | \$8402       |                          |                     |  |  |

| 0001         |            |                             | FA33   |        | STRING                                                  |              | \$FA33       |                          |                     |  |  |

| 0001         | 7          |                             | FAA0   |        | ICHAR                                                   |              | \$FAA0       |                          |                     |  |  |

| 0001         | 8          |                             | 0020   | Α      | CHARS                                                   | EQU          | \$0020       |                          |                     |  |  |

| 0001         | 9          |                             |        |        |                                                         | XREF         | ERROR,SE     | EEK,READ,WRITE,PRINT     |                     |  |  |

| 0002         | 0          |                             |        |        |                                                         | XREF         | FORMAT,      | DUMP                     |                     |  |  |

| 0002         |            |                             |        |        |                                                         | XDEF         |              | RP,TRK0,CSAVE            |                     |  |  |

| 0002         |            |                             |        |        |                                                         | XDEF         | EDONE,MI     | ERR                      |                     |  |  |

| 0002         |            |                             |        |        | •                                                       |              |              |                          |                     |  |  |

| 0002         |            |                             |        |        |                                                         |              | E PIA (POW   |                          |                     |  |  |

| 0002         |            |                             |        |        | ♦ PORT                                                  | IA=DATA F    | ORT POR      | TB=STATUS & CMD LINES    |                     |  |  |

| 0002         |            | 0000 86                     | 04     | ٨      | ♥<br>INIT                                               | LDAA         | *4           | MASK DATA DIR REGS       | $\backslash$        |  |  |

|              |            | 0000 80<br>0002 B7          |        | A<br>A | 11011                                                   | STAA         | CRA          | MASK DATA DIK REGS       |                     |  |  |

|              |            | 0002 B7<br>0005 B7          |        | A      |                                                         | STAA         | CRB          |                          |                     |  |  |

|              |            | 0003 D7                     |        | A      |                                                         | LDX          | *\$FF00      |                          |                     |  |  |

|              |            | 000B FF                     |        | A      |                                                         | STX          | PORTA        |                          |                     |  |  |

|              |            | 000E FF                     |        | Α      |                                                         | STX          | PORTB        |                          | > PIA<br>INITIALIZE |  |  |

| 0003         | 3P         | 0011 CE                     | E 0034 | Α      |                                                         | LDX          | *\$0034      | PORTA=INPUTS,CA2=0       |                     |  |  |

| 0003         | 4P         | 0014 FF                     | 8400   | Α      |                                                         | STX          | PORTA        |                          |                     |  |  |

| 0003         | 5P         | 0017 CE                     | E 3F3C | Α      |                                                         | LDX          | *\$3F3C      | PORTB 0-5 ARE OUTPUTS    |                     |  |  |

|              |            | 001AFF                      | 8402   | Α      |                                                         | STX          | PORTB        | 6&7 ARE INPUTS,MTR ON    | J                   |  |  |

| 0003         |            |                             |        |        | •                                                       |              |              |                          | /                   |  |  |

| 0003         |            |                             |        |        |                                                         |              | TION DON     |                          |                     |  |  |

| 0003         |            |                             |        |        |                                                         | ORE TO T     | RACK 0 IS    | AUTOMATIC.               |                     |  |  |

| 0004         |            | 001 007                     | 20     |        | <b>\$</b>                                               |              | ** 20        |                          |                     |  |  |

|              |            | 001D86<br>001F B7           |        | A      |                                                         | LDAA<br>STAA | *\$3C<br>CRA | CA2=1, RESTORE TO TK0    |                     |  |  |

|              |            | 001 <b>F B</b> /<br>0022 86 |        | A<br>A | TRKO                                                    | LDAA         | *\$1C        | RE,WE = 1                |                     |  |  |

|              |            | 0022 80<br>0024 B7          |        | A      | IKKO                                                    | STAA         | PORTB        | KE, WE = 1               |                     |  |  |

|              |            | 0024 D7<br>0027 86          |        | A      |                                                         | LDAA         | *\$18        | READ STATUS REG          |                     |  |  |

|              |            | 0029 B7                     |        | A      |                                                         | STAA         | PORTB        |                          |                     |  |  |

|              |            | 0022 B6                     |        | A      |                                                         | LDAA         | PORTA        | BRING STATUS             |                     |  |  |

|              |            | 002FC6                      |        | A      |                                                         | LDAB         | *\$1C        | RE=1                     |                     |  |  |

|              |            | 0031 F7                     |        | Α      |                                                         | STAB         | PORTB        |                          |                     |  |  |

| 0005         | 0P         | 0034 85                     | 04     | Α      |                                                         | BITA         | *4           | TEST TRK0                |                     |  |  |

| 0005         | 1 <b>P</b> | 0036 26                     | EA 00  | 22     |                                                         | BNE          | TRK0         |                          |                     |  |  |

| 0005         |            |                             |        |        | <ul> <li>DRIV</li> </ul>                                |              |              | – TEST READY             |                     |  |  |

|              |            | 0038 85                     |        | Α      |                                                         | BITA         | *\$80        | TEST READY               |                     |  |  |

|              |            |                             | 05 00  |        |                                                         | BNE          | INTERP       | IF RDY–GO TO IDLE LOOP   |                     |  |  |

|              |            | 003C C6                     |        | A      |                                                         | LDAB         | *0           | ERROR CODE               |                     |  |  |

| 0005         | 6 <b>P</b> | 003E BI                     | 0000   | A      |                                                         | JSR          | ERROR        |                          |                     |  |  |

Allocation of the second se

FIGURE 4

#### 4.0 WESTERN DIGITAL FD1771 CONTROLLER/FORMATTER

#### 4.1 General

The Western Digital FD1771 is a MOS/LSI device that performs the functions of a general purpose Floppy Disk Controller/Formatter. The FD1771 is compatible with the IBM 3740 Data Entry System Format, but can be programmed for variable formats.

There are two constraints for formatting with the FD1771. The first is the ID field, which must be 4 bytes long with byte 1 containing the Track Address and byte 3 containing the sector Address. The other is GAP 2 (the gap between the ID field and the Data Address Mark), which must contain 11 bytes of hex "FF" and a sync area of 6 bytes of zeros. Other gaps and data field lengths may be varied to suit individual format requirements.

### 4.2 FD1771 Interface

The FD1771 interface to the host system processor is through the 8 data lines and associated control signals.

By reading and writing selected registers within the FD1771; command, data, and status bytes are transferred between the host computer and the FD1771. This is accomplished by programming the register select pins A0, A1. For further information refer to the FD1771 data sheet.

#### 4.3 Controller Command Initiation

The FD1771 will accept eleven macro commands which perform the various disk drive functions. These commands are divided into four types and are briefly described as follow:

#### Type 1 Commands.

Restore - Causes the addressed drive to seek to track zero.

Seek - Causes the addressed drive to position the R/W head over the track specified by the host computer.

Step – Causes the drive to step one track in the direction previously selected.

Step In – Causes the drive to step one track toward track 35.

Step Out – Causes the drive to step one track toward track zero.

#### Type II Commands.

Read Command - Transfers a full sector of data, a byte at a time, to the host computer.

Write Command - Transfers a full sector of data, a byte at a time, from the host computer to the disk drive.

#### Type III Commands.

- Read Track Transfers all bytes of data on a track to the host computer. Read begins with the first index pulse encountered.

- Read Address Transfers the next encountered ID field to the host computer (Refer to Figure 1), places the Sector Address into the sector register, and checks the two byte CRC field.

- Write Track In effect, this command is the format command. The host computer must supply all gap, ID field, and data bytes with the exception of the address marks and CRC bytes.

#### Type IV Command.

Force Interrupt – Any command may be terminated and an interrupt generated by the use of this command.

In order to initiate the FD1771 commands, the host computer must load the desired command byte into the command register. Prior to this, the data register or sector register must be loaded to provide the information required by the command. Refer to Figure 5 command handshake. During a data transfer between the FD1771 and the host computer, the 'DRQ', 'RE', and 'WE' signals will comprise the handshake lines. The data transfer handshake is shown in Figure 5.

At the end of every operation a status handshake occurs where a status byte is available to the host computer. The 'INTRQ' and 'RE' lines are used in the status handshake. Refer to Figure 5 for the status handshake.

#### 4.4 Data Separation

The FD1771 is equipped with an internal data separator. But due to the fact that the internal data window is not syncronous with the serial data and can cause errors in worst case data patterns, an external separator of the type shown in Figure 3 is recommended.

The external data separator is of the type known as a 'hard' data separator. A one shot is triggered on the leading edge of the clock pulse. This 'window' extends into the middle of the bit cell. If a pulse is present in the area of the window, it is decoded as a '1' bit. Otherwise it is decoded as a zero bit.

It is possible for any data separator to get out of phase (decode clock pulses as data pulses). Therefore, a 4 bit counter is present to detect more than 3 missing clock pulses. In FM encoding the clock stream will never have more than 3 missing clock pulses in a row. Therefore, if 4 missing clock pulses occur, the data window is made to rephase on the next pulse in the stream (a clock pulse).

During address marks, the clock stream will have 3 missing clock pulses in a row. During this time data pulses are present, but due to the absence of clock pulses the data window would be terminated. Therefore, a 'false clock' circuit is present to generate a data window in the absence of clock pulses. This window is generated from the leading edge of each data pulse. If no clock pulse occurs, the trailing edge of the 'false clock' window will generate a data window to provide data decoding in the absence of clock pulses.

The required data pulse width for the FD 1771 (external separator mode) is 300 to 700 nanoseconds. Since the SA400 Drive generates a 1.2 microsecond nominal data pulse, this pulse must be reduced in width. The circuit shown in Figure 3, the pulse width has been reduced to approximately 400 nanoseconds.

| PAGE 001                 | WI         | D/400 T    | RACK DUMP    | ROUTINE        |                                    |                 |

|--------------------------|------------|------------|--------------|----------------|------------------------------------|-----------------|

| 00001                    |            |            | TTL          | WD/400 T       | RACK DUMP ROUTINE                  |                 |

| 00002                    |            |            | OPT          | CREF,REI       | L,OBJ,SYM                          |                 |

| 00003                    |            | ٠          |              |                |                                    |                 |

| 00004                    |            | <b>•</b> ( | FRACK DUM    | P ROUTINE II   | NITIATES THE READ T                | RACK            |

| 00005                    |            |            |              |                | ERS ALL THE DATA TO                |                 |

| 00006                    |            |            |              |                | GINNING AT LOC 'FF0'               |                 |

| 00007                    |            | ٦ 🔶        | Γ = TRACK D  | UMP            |                                    |                 |

| 00008                    |            | \$         |              |                |                                    |                 |

| 00009                    | 8400       |            | RTA EQU      | \$8400         |                                    |                 |

| 00010                    | 8402       | A POI      | RTB EQU      | \$8402         |                                    |                 |

| 00011                    |            |            | XREF         | POUT,PIN       | •                                  |                 |

| 00012                    |            |            | XDEF         | DUMP,D2        | ,ISAVE                             |                 |

| 00013                    |            | \$         |              |                | 0.000000                           |                 |

| 00014                    |            |            | NITIATE RE   | AD TRACK C     | OMMAND                             |                 |

| 00015                    |            |            |              | DOUT           | DODTA-OUTDUTC                      | <b>`</b>        |

| 00016P 000<br>00017P 000 |            | A DU       |              | POUT<br>*\$1B  | PORTA=OUTPUTS<br>READ TRK CMD BYTH |                 |

| 00017F 000               |            | A<br>A     | LDAA<br>STAA | PORTA          | KEAD IKK UMD DI II                 | 2               |

| 00018P 000               |            | A          | LDAB         | *\$1C          | INIT CMD                           | COMMAND         |

| 000191 000<br>00020P 000 |            | A          | STAB         | PORTB          |                                    | HANDSHAKE       |

| 00020F 000               |            | A          | LDAB         | *\$14          | WE=0                               | ANDSHAKE        |

| 000211 000<br>00022P 000 |            | A          | STAB         | PORTB          | WL-0                               |                 |

| 00022F 000               |            | A          | LDAB         | *\$1F          | A0,A1=1                            |                 |

| 00024P 001               |            | A          | STAB         | PORTB          | 10,111                             | /               |

| 00025                    | 11/0102    |            |              |                | FER DATA TO MEMOR                  | Y               |

| 00026P 001               | 7 BD 0000  | A          | JSR          | PIN            | PORTA=INPUTS                       |                 |

| 00027P 001               |            | A          | LDX          | *\$FF1         | FWA OF DATA                        |                 |

| 00028P 001               |            | A          | LDAB         | *\$1F          |                                    |                 |

|                          | F 20 0E 00 | 2F         | BRA          | DLOOP          | DATA XFER LOOP                     |                 |

| 00030P 002               | 186 IB     | A GD       | LDAA         | *\$1B          | RE=0                               |                 |

| 00031P 002               | 3 B7 8402  | А          | STAA         | PORTB          |                                    |                 |

| 00032P 002               | 6 09       |            | DEX          |                | BUMP INDEX                         | └ DATA TRANSFER |

| 00033P 002               | 7 B6 8400  | А          | LDAA         | PORTA          | GET DATA                           | / HANDSHAKE     |

| 00034P 002               | AA7 00     | А          | STAA         | 0,X            | SAVE IT                            |                 |

| 00035P 002               | C F7 8402  | А          | STAB         | PORTB          | RE=1                               |                 |

| 00036P 002               |            |            | OOP LDAA     | PORTB          | GET STATUS                         |                 |

|                          | 2 2B ED 00 |            | BMI          | GD             | DRQ=1?                             |                 |

| 00038P 003               |            | A          | BITA         | *\$40          | INTRQ SET?                         |                 |

|                          | 6 27 F7 00 |            | BEQ          | DLOOP          | DONE IF SET                        | /               |

| 00040P                   | 0.01.10    |            |              | - GET STAT     |                                    | 、<br>、          |

| 00041P 003               |            | A D2       | LDAB         | *\$1C          | ADRS STAT REG                      |                 |

| 00042P 003               |            | A          | STAB         | PORTB          | CTDODE DE                          |                 |

| 00043P 003<br>00044P 003 |            | A          | LDAB<br>STAB | *\$18<br>PORTB | STROBE RE                          | STATUS          |

| 00044P 003               |            | A<br>P     | STAB         | ISAVE          | SAVE INDEX FOR PR                  |                 |

| 00043F 004               |            | г<br>А     | LDAA         | PORTA          | GET STAT BYTE                      |                 |

| 00040P 004               |            | A          | LDAA         | *\$1C          | STAT HANDSHAKE                     | /               |

| 00047F 004               |            | A          | STAB         | PORTB          | STILL HIM (DOLLARD                 | /               |

| 000481 004<br>00049P 004 |            | 2 <b>a</b> | COMA         | ICRID          | INVERT STAT BYTE                   |                 |

| 00050P 004               |            | А          | JSR          | STATUS         | REPORT STATUS                      |                 |

| 00051P 005               |            |            | RTS          |                | RETURN                             |                 |

| 00052                    |            | \$         |              |                |                                    |                 |

| 00053P 005               | 2 0000     | A ISA      | VE · FDB     | 0              | INDEX SAVE                         |                 |

| 00054                    | a          |            | END          |                |                                    |                 |

|                          | RORS 00000 |            |              |                |                                    |                 |

|                          |            |            |              |                |                                    |                 |

REFERENCE AND A COMPANY OF STREET

. .

# FIGURE 5

## 5.0 HARDWARE AND SOFTWARE CONSIDERATIONS

#### 5.1 General

In using the FD1771, it is important to note that the 'DRQ' and 'INTRQ' lines are open drain outputs and must be pulled up. The recommended value is a 10K OHM resistor to +5V.

The FD1771 data lines are active low outputs/inputs. Therefore, when programming with the PIA; all command, data, and status bytes must be inverted. This may be accomplished either by the software, or by adding inverters between the PIA port 'A' (Figure 3) and the FD1771 data lines.

435 Oakmead Parkway, Sunnyvale, California 94086 Phone: (408) 733-0100 TWX: 910 339 9355 SHUGART SUVL

PRINTED IN U.S.A.